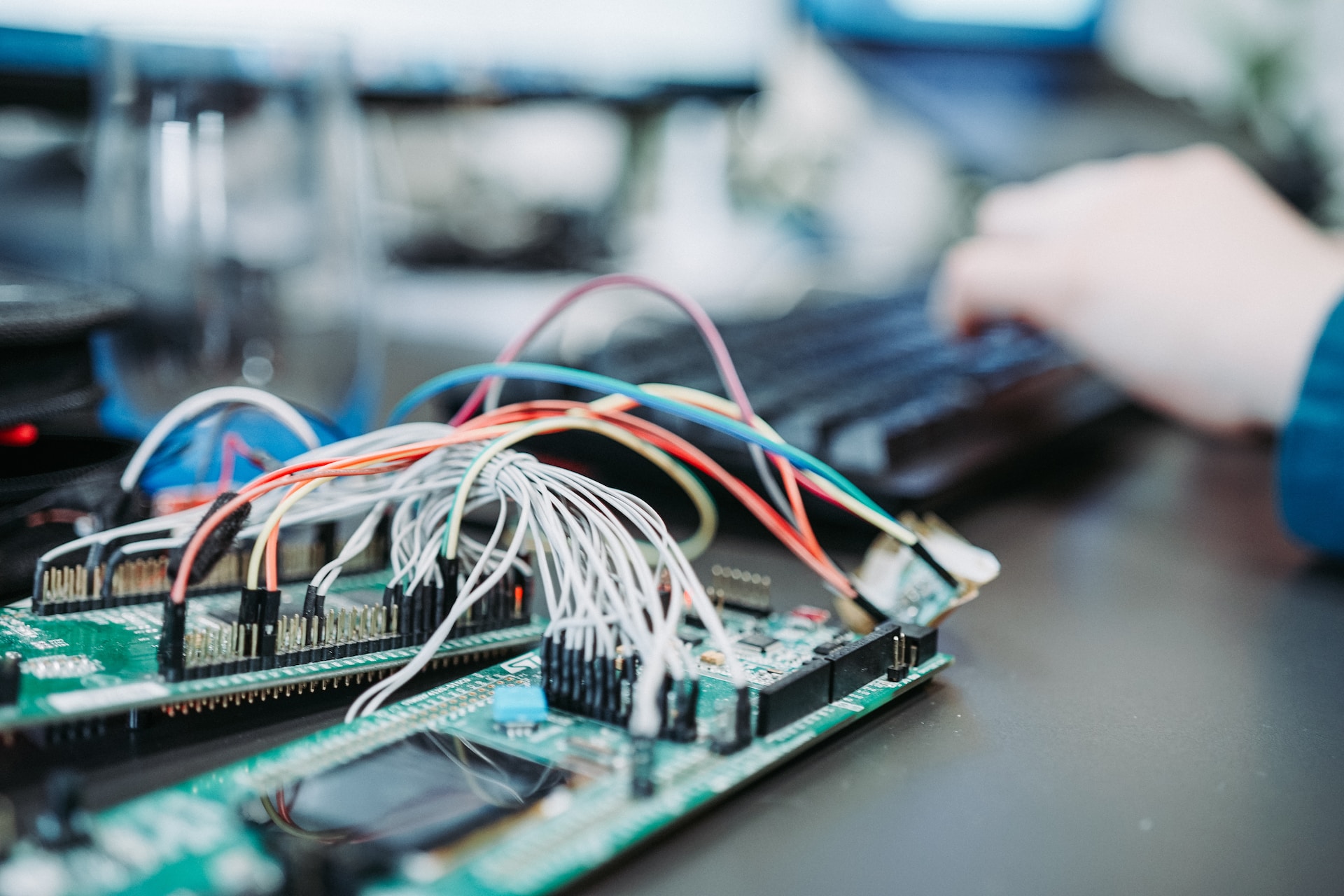

FPGA memory accessible from Vivado

The ability to easily access or modify the contents of a memory instantiated in FPGA chip via a computer can be very helpful during verification or debugging. In case of AMD/Xilinx chips and Vivado IDE, this can be achieved using a combination of several IPs and Tcl commands.