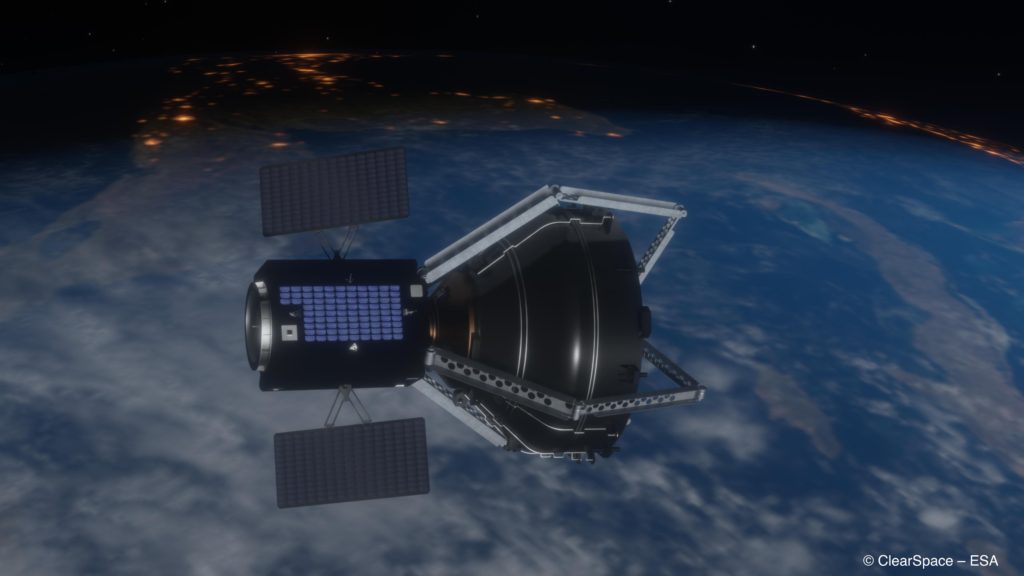

Design, development and verification of a RendezVous Sensors Processing Unit (RVSPU) subsystem for space debris removal satellite. Designed a flexible and configurable architecture for high reliability and quick emergency response. Project developed for the ClearSpace start-up founded by European Space Agency (ESA).

| Languages | VHDL, Tcl |

| Tools | ModelSim, Riviera Pro, Libero SoC |

| Target | not disclosed |

| Time frame | 10.2021 – 07.2022 |

| Commercial | ✔ |

| Collaboration | SYDERAL Polska, SYDERAL Swiss, ClearSpace |

Project goals

- Analyze and report corrections for the requirements of one of the subsystems of the first active debris removal mission: ClearSpace-1

- Design and develop the FPGA-based subsystem meeting the current requirements

- Flexible architecture to easily incorporate the not-yet-defined requirements/features in the future

- High fault tolerance design

- Triple Modular Redundancy (TMR) for higher hardware fault tolerance

- Error detection and correction (EDAC) schemes incorporated for higher reliability of memories

My responsibilities

- Requirements consultant

- Reporting requirements errors/suggesting corrections

- General architecture development

- General architecture modifications to accommodate requirements’ updates

- Resource utilization optimization

- Architecture, submodules and verification documentation

- Development and implementation of flexible and configurable top-level architectures

- Development and implementation of multiple flexible and configurable submodule’s architectures (such as the Configurable architecture for multiple measurements thresholds detection)

- Verification of multiple submodules