Here you can find more information about my professional experience

My primary areas of interest are digital control systems design, HDL development and task automation. I have worked with FPGA chips from vendors like Intel (Altera), Xilinx and Microchip (Microsemi) and used multiple industry standard tools like HDL simulators. I also automate the development workflow by implementing CI systems and automation scripts.

Previous Areas of Work

Industry

I have experience in designing and debugging reliable as well as flexible control systems for the industry. There is a good chance that I have been involved in the design or development of generators which powered the machines producing things you are using.

Space Sector

Experience in Space industry is very important – especially in terms of HDL design verification and documentation. I have developed multiple sub-blocks and designed a whole systems as well as created simulation models for control system verification.

Integrated Circuits

My academic work is focused on digital integrated circuits design. Each thesis I have written involved HDL design. The MSc project has been commercialized and implemented in an actual chip. My PhD project, that I’m working on, is intended for silicon implementation.

Quantum Systems Equipment

During PhD studies as well as my commercial work I was involved in the design and development of apparatus for quantum systems. I had a chance to contribute i.e. to quantum information experiments control system and to quantum key distribution system.

Selected projects I’ve worked on in the past

Low latency 100 Gbps communication system

Development and verification of a high data rate and low latency communication system using Xilinx GTY transceivers in Virtex UltraScale+ FPGA. Designed for inter-FPGA transmission with close to maximum line rates and minimum possible latency. Verified in hardware using Xilinx VCU128 Evaluation Kit.

ClearSpace-1 subsystem architecture

Design, development and verification of a RendezVous Sensors Processing Unit (RVSPU) subsystem for space debris removal satellite. Designed a flexible and configurable architecture for high reliability and quick emergency response. Project developed for the ClearSpace start-up founded by European Space Agency (ESA).

SpaceFibre Image Compression

Development and verification of a demonstrator of SpaceFibre technology usage for hyperpectral image processing applications using SHyLoC, CCSDS-121, CCSDS-123 IPs. Designed for a high-performance FPGA evaluation board and verified with data transmission speeds up to 2.5 Gbps. Project developed for the European Space Agency (ESA).

Configurable plasma power supply control system

Design, development and verification of measurement and control system aimed for high-power multi-output plasma power generators intended for PVD and PECVD processes. Enables outputs number modification during operation (through configuration registers) as well as at compilation stage (through implementation parameters – for resource usage reduction). The designed architecture supports multiple devices (with any number of outputs) connection for synchronization and cooperation.

Multiple power supplies synchronization and cooperation system

Design, implementation, integration and verification of a set of features for multiple power generators connection. The system enables synchronization of multiple independent devices (or outputs) or allows to achieve results similar to single higher power supply or a combination of both. Implemented as additional functionality to existing configurable plasma power supply control system architecture.

MBIST – Memory Built-In Self Test

Memory Built-In Self Test (MBIST) design used for automatic fault detection in single-port as well as dual-port SRAM memories. Intended for implementation as part of ASIC (Application-Specific Integrated Circuit) designs. Developed as part of the Master’s Thesis. Implemented in Verilog HDL.

Dual port SRAM memory model with faults simulation

Generic, behavioral, dual-port memory model design with delay and functional SRAM faults simulation. Developed in order to verify the implemented Memory Built-In Self Test (MBIST) block – created for Static-Random Access Memories verification. Implemented in Verilog HDL.

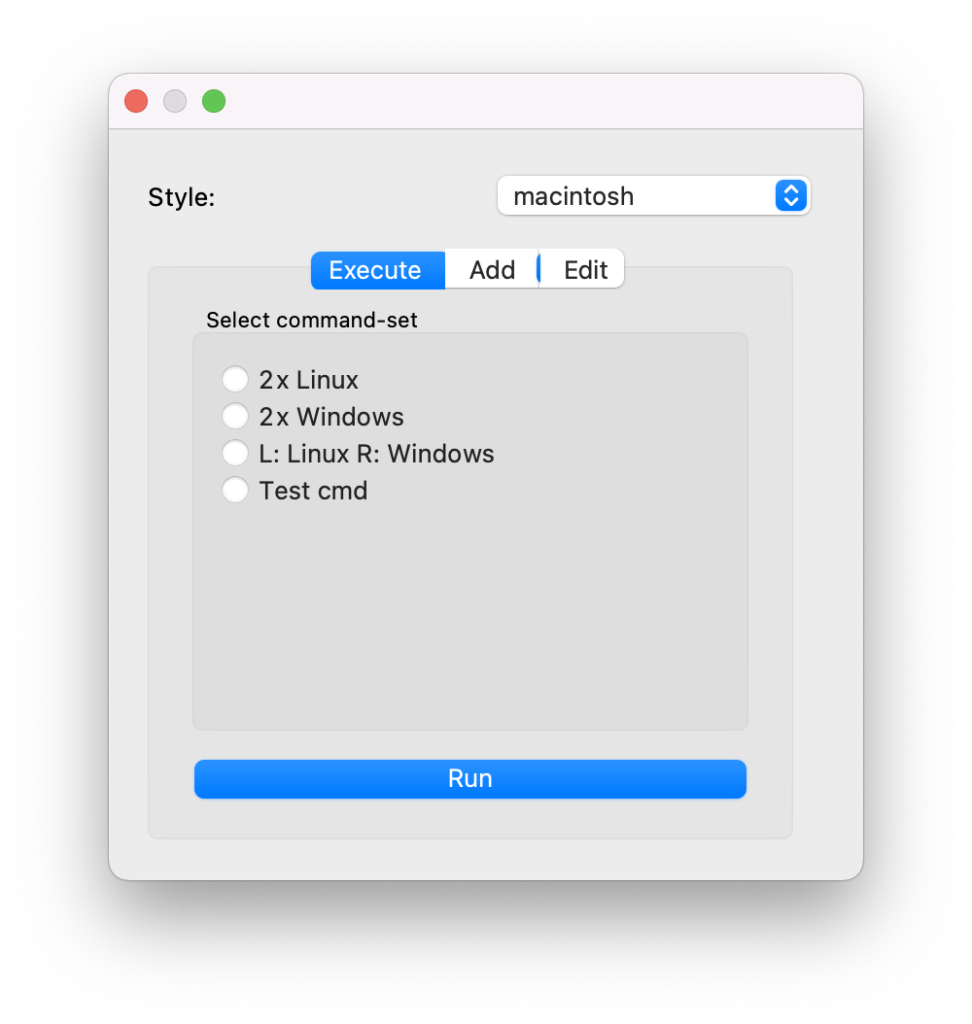

Simple Command Runner

A very simple Python GUI program for easy execution of sets of commands defined in dedicated XML file. Works on Linux, Windows and MacOS. Used for quick selection and automation of tedious tasks – like switching monitors’ inputs.