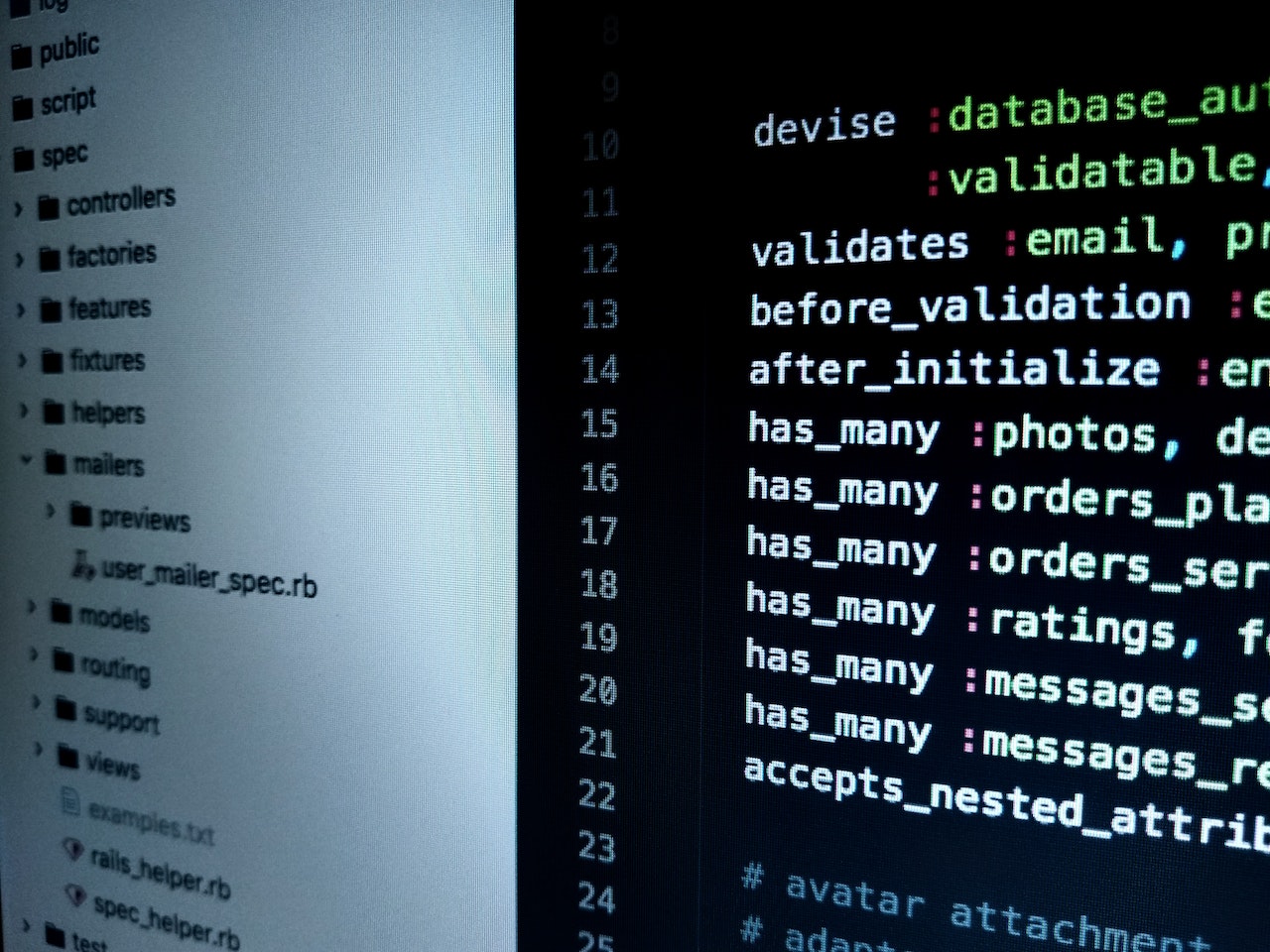

How to get disassembled ELF file in Vivado/Vitis

Sometimes we need to debug a module containing a microprocessor implemented in FPGA. Often the program is enclosed in ELF file – leaving us with no access to the program source code. In these cases we can learn how the program functions by analyzing the machine code for the microprocessor. But first, the assembly code needs to be extracted from the ELF file. Let me show you how to get disassembled code from ELF file in Vivado/Vitis.