Development and verification of a high data rate and low latency communication system using Xilinx GTY transceivers in Virtex UltraScale+ FPGA. Designed for inter-FPGA transmission with close to maximum line rates and minimum possible latency. Verified in hardware using Xilinx VCU128 Evaluation Kit.

| Languages | VHDL, Tcl |

| Tools | Vivado |

| Target | Virtex UltraScale+ |

| Time frame | 10.2022 – 04.2023 |

| Commercial | ✔ |

| Project Owner | FastLogic |

Project goals

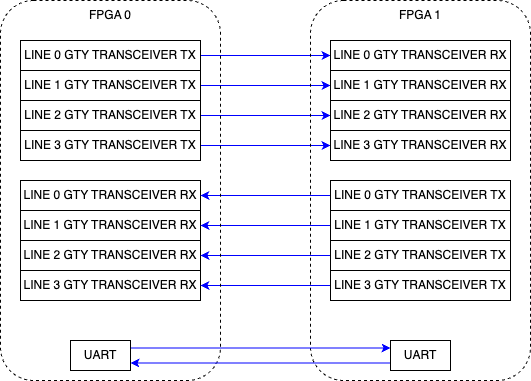

- Design a link layer point-to-point communication system utilizing GTY transceivers

- Self-synchronous communication – the data stream contains both the data and the clock

- Communication channel supports between 1 and 4 individual line (up to full Quad)

- Each line operating at 25 Gbps line rate

- Minimize data latency as much as possible

- Automatic channel initialization

- Auxiliary low-speed UART connection for initialization

- Low Bit Error Rate

Single channel connection

Channel initialization stages

Block Synchronization:

- Performed for each line individually

- Changing data alignment until expected value detected

- Continuous monitoring

Channel Bonding:

- Different lines’ latency compensation

- Uses custom elastic buffers and dedicated controller

- Lowest possible delay

Dynamic Scrambling:

- Additional transmitted data encoding

- The same data is scrambled differently each time

Achieved results

- Hardware verified using Xilinx VCU128 Evaluation Kit

- Automatic hardware verification using custom Tcl scripts

- 0 bit errors detected during 36 000 restarts

- Approximately 80% lower latency compared to the Aurora 64/66B Protocol

My responsibilities

- General architecture design and implementation

- IP cores generation and configuration

- Simulation verification

- Design optimization

- Debugging

- Debug functionalities implementation

- Hardware verification

- Refactoring/Clean-up (warnings removal etc.)

- Automatization scripts implementation in Tcl

- Concept, implementation and verification documentation in LaTeX