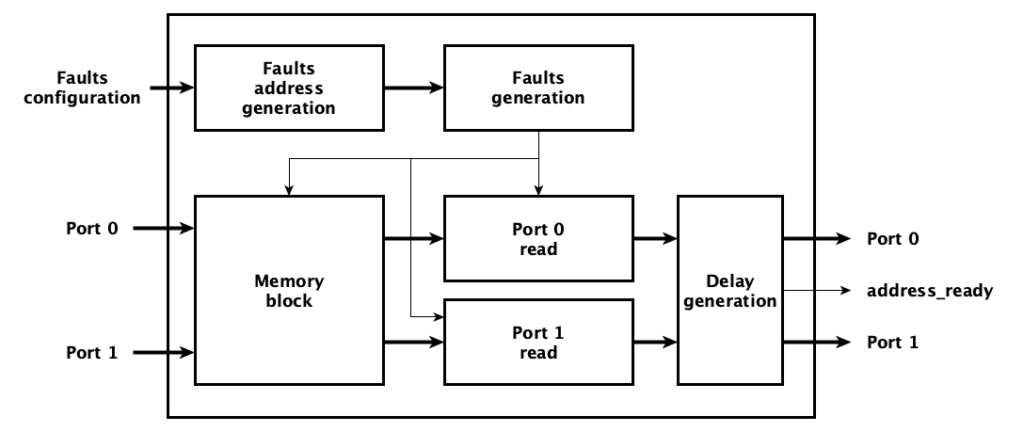

Generic, behavioral, dual-port memory model design with delay and functional SRAM faults simulation. Developed in order to verify the implemented Memory Built-In Self Test (MBIST) block – created for Static-Random Access Memories verification. Implemented in Verilog HDL.

| Language | Verilog |

| Tools | ModelSim |

| Target | none – behavioral model for MBIST verification |

| Time frame | 12.2017 – 02.2019 |

| Commercial | ✘ |

| Collaboration | – |

Selected features of the implemented SRAM model

- 2 parallel read and write ports

- Random read and write access delays simulation – to simulate various connection types

- Implemented 83 different SRAM fault primitives: 27 single-cell and 56 multi-cell.

- Easy to implement additional fault models – including for other memory types

- Physical memory state visualization – including number of words in a single row of memory cells

Configurable parameters

- Address port width – influence maximum memory depth

- Data port width – influence memory word width

- Physical memory architecture – number of words in a single row of memory cells

- Maximum operation delay – both read and write

- Maximum number of simultaneous simulated memory faults models

- Enable or disable memory fault models simulation

- Memory address space definition

- Number of simulated fault models of a given type

- Victim cell position: random or manually selected

- Aggressor cell position: random or manually selected one of victim neighboring cells

- Maximum data retention time in – for DRF fault model

Implemented SRAM fault models:

| # | Fault model | Fault model name | Fault primitive |

| 1 | SAF | Stuck-at fault | < ∀/0/− >, < ∀/1/− > |

| 2 | TF | Transition fault | < w ↑ /0/− >, < w ↓ /1/− > |

| 3 | RDF | Read destructive fault | < r0/ ↑ /1 >, < r1/ ↓ /0 > |

| 4 | DRDF | Deceptive read destructive fault | < r0/ ↑ /0 >, < r1/ ↓ /1 > |

| 5 | IRF | Incorrect read fault | < r0/0/1 >, < r1/1/0 > |

| 6 | RRF | Random read fault | < r0/0/? >, < r1/1/? > |

| 7 | DRF | Data retention fault | < 1T / ↓ /− >, < 0T / ↑ /− >, < 1T/?/− >,< 0T/?/− > |

| 8 | NAF | No access fault | {< w ↑ /0/− >, < w ↓ /1/− >, < r0/0/? >, < r1/1/? >} |

| 9 | USF | Undefined state fault | < w0/?/− >, < w1/?/− >, < r0/?/? >, < r1/?/? > |

| 10 | CFds | Disturb coupling fault | < wx; 0/ ↑ /− >, < wx; 1/ ↓ /− >, < rx; 0/ ↑ /− >, < rx; 1/ ↓ /− > |

| 11 | CFst | State coupling fault | < 1; 1/0/− >, < 1; 0/1/− >, < 0;1/0/− >,< 0;0/1/− > |

| 12 | CFir | Incorrect read coupling fault | < 0; r0/0/1 >, < 0; r1/1/0 >, < 1; r0/0/1 >, < 1; r1/1/0 > |

| 13 | CFrr | Random read coupling fault | < 0; r0/0/? >, < 0; r1/1/? >, < 1; r0/0/? >, < 1; r1/1/? > |

| 14 | CFdr | Deceptive read destructive coupling fault | < 0; r0/ ↑ /0 >, < 0; r1/ ↓ /1 >, < 1; r0/ ↑ /0 >, < 1; r1/ ↓ /1 > |

| 15 | CFrd | Read destructive coupling fault | < 0; r0/ ↑ /1 >, < 0; r1/ ↓ /0 >, < 1; r0/ ↑ /1 >, < 1; r1/ ↓ /0 > |

| 16 | CFtr | Transition coupling fault | < 0; w ↓ /1/− >, < 0; w ↑ /0/− >, < 1; w ↓ /1/− >, < 1; w ↑ /0/− > |

| 17 | wDRDF&wDRDF | Weak deceptive read destructive fault & weak deceptive read destructive fault | < r0 : r0/ ↑ /0 >, < r1 : r1/ ↓ /1 > |

| 18 | wRDF&wRDF | Weak read destructive fault & weak read destructive fault | < r0 : r0/ ↑ /1 >, < r1 : r1/ ↓ /0 > |

| 19 | wRDF&wTF | Weak read destructive fault & weak transition fault | < r0 : w ↑ /0/− >, < r1 : w ↓ /1/− > |

| 20 | wCFds&wCFds | Weak disturb coupling fault & weak disturb coupling fault | < w0 : rd; 0/ ↑ /− >, < w0 : rd; 1/ ↓ /− >, < w1 : rd; 0/ ↑ /− >, < w1 : rd; 1/ ↓ /− >, < r0 : r0; 0/ ↑ /− >, < r0 : r0; 1/ ↓ /− >, < r1 : r1; 0/ ↑ /− >, < r1 : r1; 1/ ↓ /− > |

| 21 | wCFdr&wDRDF | Weak deceptive read destructive coupling fault & weak deceptive read destructive fault | < 0; r0 : r0/ ↑ /0 >, < 0; r1 : r1/ ↓ /1 >, < 1; r0 : r0/ ↑ /0 >, < 1; r1 : r1/ ↓ /1 > |

| 22 | wCFrd&wRDF | Weak read destructive coupling fault & weak read destructive fault | < 0; r0 : r0/ ↑ /1 >, < 0; r1 : r1/ ↓ /0 >, < 1; r0 : r0/ ↑ /1 >, < 1; r1 : r1/ ↓ /0 > |

| 23 | wCFds&wRDF | Weak disturb coupling fault & weak read destructive fault | < w0 : r0/ ↑ /1 >, < w0 : r1/ ↓ /0 >, < w1 : r0/ ↑ /1 >, < w1 : r1/ ↓ /0 > |

| 24 | wCFds&wIRF | Weak disturb coupling fault & weak incorrect read fault | < w0 : r0/0/1 >, < w0 : r1/1/0 >, < w1 : r0/0/1 >, < w1 : r1/1/0 > |

| 25 | wCFds&wRRF | Weak disturb coupling fault & weak random read fault | < w0 : r0/0/? >, < w0 : r1/1/? >, < w1 : r0/0/? >, < w1 : r1/1/? > |

References

- A. A. Wojciechowski, K. Marcinek and W. A. Pleskacz, „Configurable MBIST Processor for Embedded Memories Testing,” 2019 MIXDES – 26th International Conference „Mixed Design of Integrated Circuits and Systems”, Rzeszów, Poland, 2019, pp. 341-344.

- Said Hamdioui, J. van de Goor, “Efficient Tests for Realistic Faults in Dual-Port SRAMs,” IEEE TRANSACTIONS ON COMPUTERS, vol. 51, no. 5, 2002.

- Said Hamdioui, Testing Static Random Access Memories: Defects, Fault Models and Test Patterns. Springer Science+Business Media, LCC, 2004.