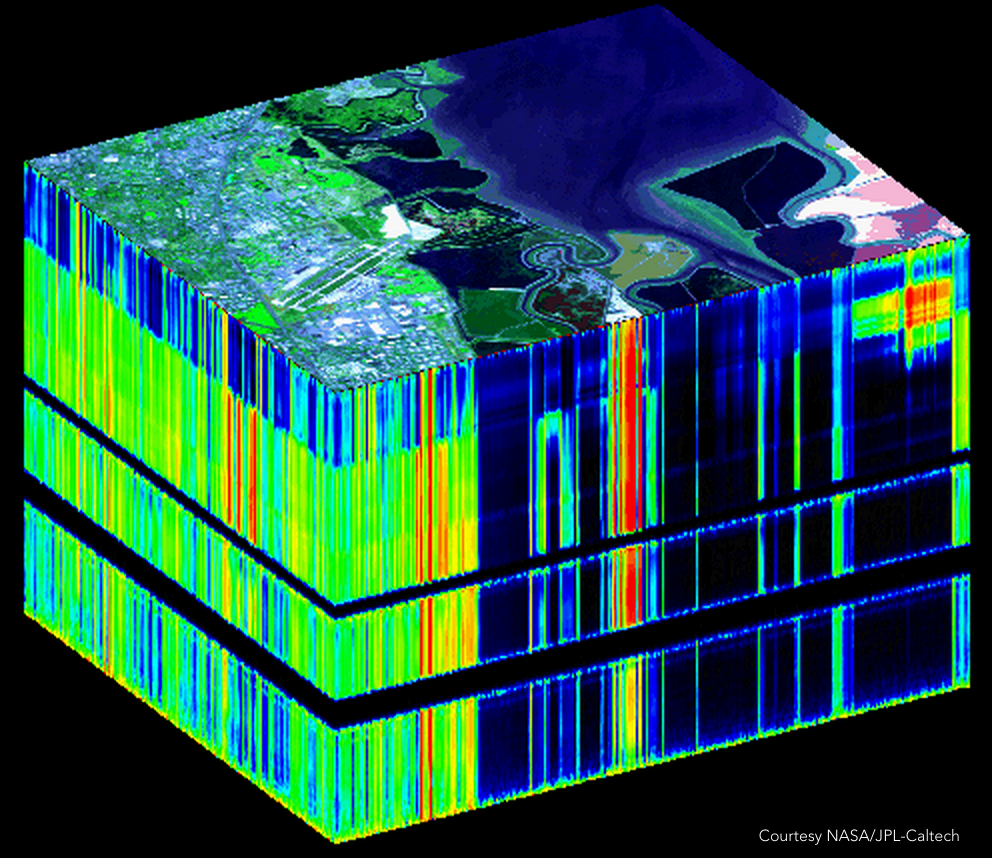

Development and verification of a demonstrator of SpaceFibre technology usage for hyperpectral image processing applications using SHyLoC, CCSDS-121, CCSDS-123 IPs. Designed for a high-performance FPGA evaluation board and verified with data transmission speeds up to 2.5 Gbps. Project developed for the European Space Agency (ESA).

| Languages | VHDL, Tcl |

| Tools | ModelSim, Riviera Pro, Libero SoC |

| Target | Microsemi RTG4 |

| Time frame | 03.2020 – 12.2020 |

| Commercial | ✔ |

| Collaboration | SYDERAL Polska, Thales Alenia Space Espana (TAS-E), European Space Agency (ESA) |

Project goals

- Demonstrate a parallel operation of CCSDS-121 and CCSDS-123 compatible multispectral image compression IP cores on a high-performance FPGA evaluation board

- Combine the CCSDS-123 and CCSDS-121 IP cores, demonstrate parallel operation of image compression algorithms, thus serving as a baseline for future developments in this technological area

- Show the SpaceFibre interface as a high-throughput data transfer interface used to transmit hyperspectral images to the CCSDS-121 and CCSDS-123 compression cores to perform on-the-fly image compression

- Receive hyperspectral images to be compressed through SpaceFibre interface (2.5 Gbps)

- Images in Band Interleaved by Pixel format (BIP)

- Send back compressed image through SpaceFibre interface

- Use different SpaceFibre virtual channels for both compression cores (VC1 and VC2)

- Allow configuration of compression IP cores through SpaceWire RMAP (100 Mbps) or SpaceFibre VC0 interface

Compression Modes

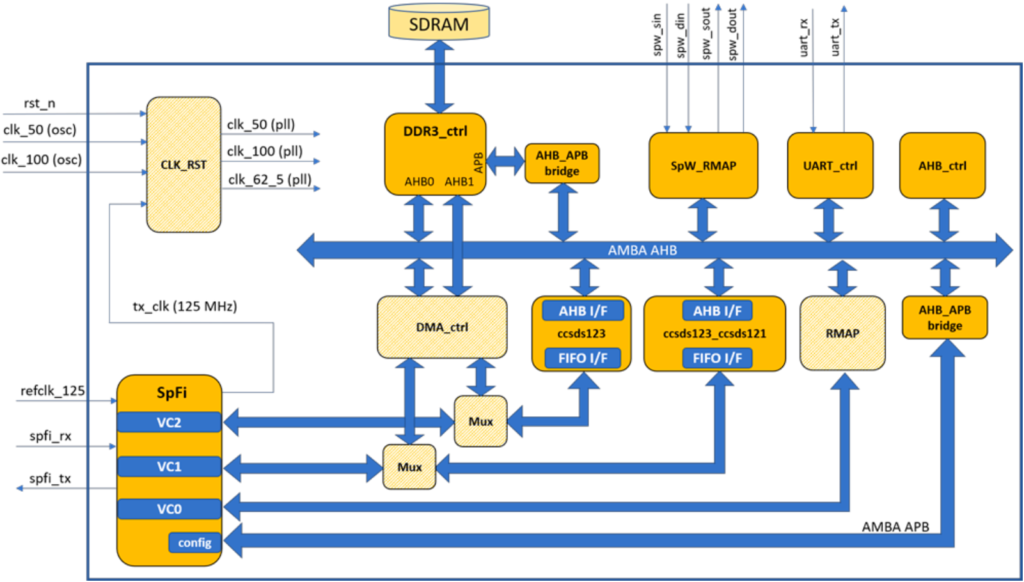

Online mode (on-the-fly):

- Image data received through the SpFi interface is transmitted directly to one of the compression cores

- Data compression in the selected compression core

- Compressed data is returned on the same SpFi virtual channel

- Simultaneous online compression using both compression cores is allowed

Offline mode:

- Image data received through the SpFi or SpWi interface is stored in the external DDR memory

- A DMA controller reads from the memory and writes to one of the compression cores

- Compressed data is stored back in the external memory

- The compressed data is read from the external memory with SpW or SpFi VC0 (RMAP)

SpaceFibre Image Compression – general architecture

My responsibilities

- General architecture implementation

- Requirements specification clarification

- Compression IP cores implementation

- Compression IP cores configuration

- DMA controller implementation and verification

- Verification tests specification and implementation

- Debugging

- Architecture and verification documentation

References

- Demonstration of SpaceFibre Technology Usage for Image Processing Applications – Final Presentation Days 1st June 2021

- Demonstration of SpaceFibre Technology Usage for Image Processing Application – Abstract

- SYDERAL Polska post on LinkedIn

- Post on LinkedIn about talk on SEFUW

- 5th SEFUW 2023 presentation

- 5th SEFUW 2023 presentation page